This post defines and describes the expression 100GBASE-R for 100Gbps Ethernet Applications.

What does the expression 100GBASE-R Mean?

For Ethernet applications, the IEEE 802.3 standard states that the term 100GBASE-R represents a group (or family) of Physical Layer (e.g., 100Gbps Transceiver) devices that do the following:

- When it transmits its data towards the PMD (Physical Medium Dependent) device, it will:

- Encode the CGMII data into the 64B/66B PCS (Physical Coding Sublayer) code.

- This is what the -R suffix means, by the way.

- Divide (or de-multiplex) its outbound traffic into 20 PCS Lanes by routing each 66b (66 bit) block to a different PCS lane (in a round-robin manner).

- It will often multiplex these 20 PCS Lanes into 4 or 10 physical (or electrical) lanes for CAUI-4 and CAUI-10 applications, as it transports this data to an Optical Transceiver (or PMD), respectively.

- When it receives data (from the PMD), it will:

- De-multiplexes these CAUI-4/CAUI-10 physical (or electrical) lanes of traffic that it receives from the Optical Transceiver into 20 PCS Lanes.

- Combines (or multiplexes) these 20 PCS Lanes into a single stream of traffic as it routes this data towards the MAC (Media Access Control) device.

- Decodes this data from the 64B/66B PCS code back into the CGMII (100Gbps Media Independent Interface) format.

NOTE: I discuss some of this processing (with 100GBASE-R data) for ITU-T G.709, Annex E mandated handling (before GMP Mapping this data into the OPU4 Payload) in Lesson 10; within THE BEST DARN OTN TRAINING PRESENTATION…PERIOD!!!

In Summary

In summary, these 100Gbps Ethernet devices will encode their “outgoing” data into the 64B/66B PCS code before transmitting it over some media.

These 100Gbps Ethernet devices will also decode their “incoming” data from the 64B/66B PCS code (to restore the data to its original CGMII content) as it receives this data.

In other words, the 100Gbps Ethernet system will encode this data into the 64B/66B PCS format solely to transport this data across the communication media.

Once this Ethernet data has arrived (at the other end of the media), the Ethernet system will decode this data (from the 64B/66B PCS format) to restore it to its original content.

The bit rate of this 64B/66B PCS encoded 100Gbps Ethernet data stream is 103.125Gbps ‡ 100pm.

Why Do We Encode our 100Gbps Ethernet Data into this 64B/66B PCS Code before we transmit this data over Optical Fiber?

We encode this 100Gbps Ethernet (CGMII) data into this 64B/66B PCS Code before we:

- Transmit this data over Optical Fiber, or

- Map this data into an OPU4 Frame (again for transmission over Optical Fiber).

There are several reasons we encode this data (before transmission over Optical fiber). But the main goals are to convert this data into a more conducive format for transport over Optical Fiber. More specifically, by converting this data into the 64B/66B code, we:

- Minimize Running Disparity (e.g., maintain DC balance) with our data, and

- Ensure that we have no long strings of consecutive “1s” or consecutive “0s” within the data, we transport over Optical Fiber.

- Offer greater management capability (within our 100Gbps signal) by including Sync Bits within our 66-bit blocks. These Sync bits permit us to designate certain 66-bit blocks as data blocks and other 66-bit blocks as control blocks. I discuss some of this in detail in Lesson 10 within THE BEST DARN OTN TRAINING PRESENTATION…PERIOD!!!

Clueless about OTN? We Can Help!!! Click on the Banner Below to Learn More!!!

Discounts Available for a Short Time!!

The Various 100GBASE-R Transceiver Devices

IEEE 802.3 also states that the Physical Layer (Transceiver devices) supporting the following standards must support the 100GBASE-R PCS encoding/decoding scheme.

- 100GBASE-CR4

- 100GBASE-CR10

- 100GBASE-SR4

- 100GBASE-SR10

- 100GBASE-KP4

- 100GBASE-KR4

- 100GBASE-LR4

- 100GBASE-ER4

Please check out the post on 64B/66B encoding to learn more about that encoding scheme.

Where is this PCS Encoder/Decoder Located?

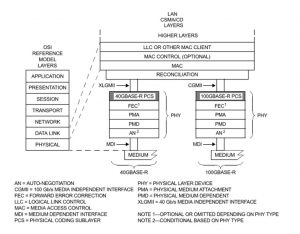

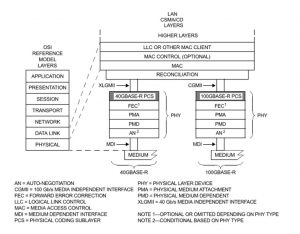

IEEE 802.3 states that the 100GBASE-R PCS block (e.g., the entity that performs the PCS Encoding/Decoding) resides between the Reconciliation Layer and the PMA (Physical Medium Attachment), as shown in Figure 1 below.

Figure 1, Architectural Positioning of 100Gigabit Ethernet (from the IEEE 802.3 Standard)

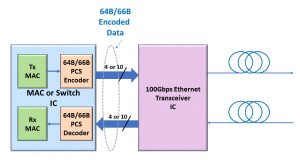

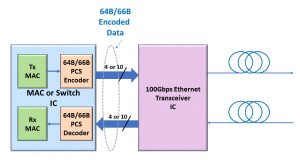

But, in a real system, this PCS Encoder/Decoder often resides in the same IC containing the MAC (Media Access Controller).

Figure 2 illustrates a MAC that includes the PCS Encoder and Decoder functions.

Figure 2, Illustration of a Connection between the MAC and a 100Gbps Transceiver IC

This figure also shows the MAC or Switch IC exchanging data with the 100Gbs Ethernet Transceiver IC over a CAUI-4 or CAUI-10 Interface.

Has Inflation got You Down? Our Price Discounts Can Help You Fight Inflation and Help You Become an Expert on OTN!! Click on the Banner Below to Learn More!!!

Temporary Discounts Available Now!!